-

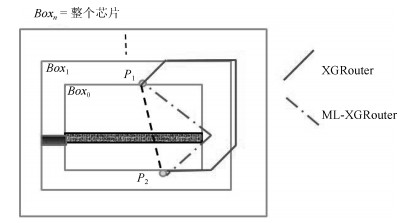

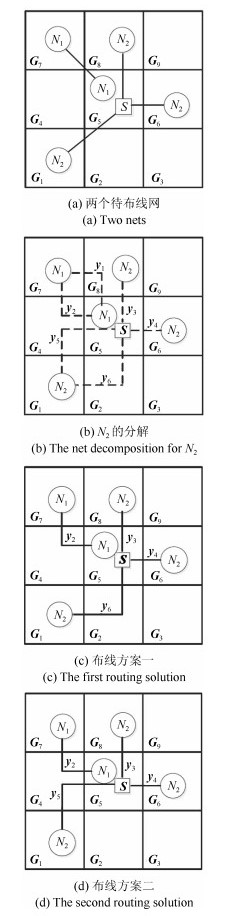

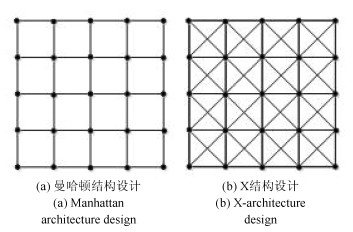

摘要: X结构带来物理设计诸多性能的提高, 该结构的引入和多层工艺的普及, 使得总体布线算法更复杂.为此, 在XGRouter布线器的基础上, 本文设计了三种有效的加强策略, 包括: 1)增加新类型的布线方式; 2)粒子群优化(Particle swarm optimization, PSO)算法与基于新布线代价的迷宫布线的结合; 3)初始阶段中预布线容量的缩减策略, 继而引入了多层布线模型, 简化了XGRouter的整数线性规划模型, 最终构建了一种高性能的X结构多层总体布线器, 称为ML-XGRouter.在标准测试电路的仿真实验结果表明, ML-XGRouter相对其他各类总体布线器, 在多层总体布线中最重要的优化目标——溢出数和线长总代价两个指标上均取得最佳.Abstract: The introduction of X-architecture can improve many performance standards of the chip in physical design. The proposed X-architecture and pervasive multilayer technology make the global routing problem more complex. For this reason, this paper presents the following enhancements based on XGRouter: 1) the introduction of some new types of routing; 2) the combination of particle swarm optimization (PSO) algorithm and maze routing with new routing cost; 3) a reduction strategy of routing capacity in the initial stage. Then the multilayer routing model is introduced and the integer linear programming model of XGRouter is simplified. Finally, a high performance X-architecture multilayer global router, namely ML-XGRouter, is proposed. The experimental results on benchmark circuits have shown that our proposed ML-XGRouter is effective and superior to state-of-the-art multilayer routing algorithms on overflows and the total cost of wirelength, which are the two most important optimization goals for the multilayer global routing problem.

-

Key words:

- X-architecture /

- multilayer routing /

- very large scale integration (VLSI) /

- global routing /

- particle swarm optimization (PSO)

1) 本文责任编委 王鼎 -

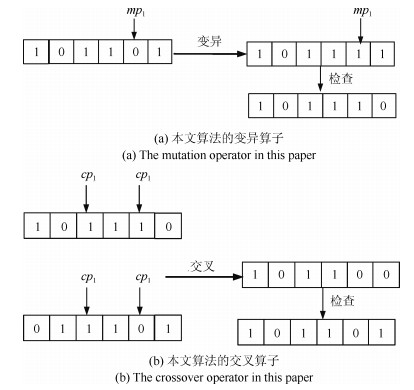

图 8 图 7(b)中布线实例的编码图

Fig. 8 The encoding for the routing instance in Fig. 7 (b)

表 1 未采用和采用E1策略(E2策略)的布线结果对比

Table 1 Comparison of routing results without and with E1 strategy (E2 strategy)

基准 E0 E1 减少率(%) E2 减少率(%) 电路 TOF TWL TOF TWL TOF TWL TOF TWL TOF TWL 11 85 46.7 85 46.9 0 -0.43 0 47.9 100 -2.57 12 75 45.9 70 45.8 6.67 0.22 0 46.6 100 -1.53 13 44 127.1 34 127.2 22.73 -0.08 0 128.9 100 -1.42 14 12 110.8 7 110.9 41.67 -0.09 0 111 100 -0.18 15 32 130.8 29 131.4 9.38 -0.46 0 130.3 100 0.38 16 2 33.9 1 33.9 50 0 0 33.9 100 0 17 0 63.4 0 63.3 0 0.16 0 63.5 0 -0.16 18 3 779 80 3 682 80 2.57 0 3 170 80.8 16.12 -1 AVG 16.63 -0.09 77.01 -0.81 表 2 在E1策略(E2策略)的基础上未采用和采用E3策略的布线结果对比

Table 2 Comparison of routing results without and with E3 strategy, on the basis of E1 strategy (E2 strategy)

基准 E1 E1+E3 减少率(%) E2 E2+E3 减少率(%) 电路 TOF TWL TOF TWL TOF TWL TOF TWL TOF TWL TOF TWL 11 85 46.9 68 46.4 20 1.07 0 47.9 0 47.5 0 0.84 12 70 45.8 49 44.4 30 3.06 0 46.6 0 45.6 0 2.15 13 34 127.2 27 123.7 20.59 2.75 0 128.9 0 127.4 0 1.16 14 7 110.9 7 110.2 0 0.63 0 111 0 110.7 0 0.27 15 29 131.4 13 127.7 55.17 2.82 0 130.3 0 129.8 0 0.38 16 1 33.9 1 33.9 0 0 0 33.9 0 34 0 -0.3 17 0 63.3 0 63 0 0.47 0 63.5 0 64.2 0 -1.1 18 3 682 80 3 226 80.5 12.38 -0.63 3 170 80.8 3 165 81 0.16 -0.25 AVG 17.27 1.27 0.02 0.39 表 3 在E1和E2策略共同作用的基础上未采用和采用E3策略的布线结果对比

Table 3 Comparison of routing results without and with E3 strategy, on the basis of E1 and E2 strategies

基准 E1+E2 E1+E2+ E3 减少率(%) 电路 TOF TWL TOF TWL TOF TWL 11 0 47.8 0 47 0 1.67 12 0 46.5 0 45 0 3.23 13 0 128.8 0 124.6 0 3.26 14 0 110.9 0 110.1 0 0.72 15 0 130.2 0 126.8 0 2.61 16 0 33.9 0 33.9 0 0 17 0 63.4 0 63.1 0 0.47 18 3 106 80.8 2 762 81.1 11.08 -0.37 AVG 1.38 1.45 表 4 在ISPD98测试电路的属性及初始布线的结果

Table 4 ISPD98 benchmark circuits and the results of the initial stage

基准电路初始布线情况 名称 网格大小 线网数 bf.nets af.nets Ratio (%) ibm01 64 $\times$ 64 11 507 25 698 20 127 78.32 ibm02 80 $\times$ 64 18 429 55 739 39 871 71.53 ibm03 80 $\times$ 64 21 621 43 272 30 181 69.75 ibm04 96 $\times$ 64 26 163 49 821 34 193 68.63 ibm06 128 $\times$ 64 33 354 75 912 59 812 78.79 ibm07 192 $\times$ 64 44 394 97 391 69 123 70.97 ibm08 192 $\times$ 64 47 944 121 912 89 134 73.11 ibm09 256 $\times$ 64 50 393 115 871 91 268 78.77 ibm10 256 $\times$ 64 64 227 169 391 113 459 66.98 AVG 72.98 表 5 在ISPD07测试电路的属性及初始布线的结果

Table 5 ISPD07 benchmark circuits and the results of the initial stage

基准电路初始布线情况 名称 网格大小 线网数 bf.nets af.nets e3.af.nets Ratio (%) e3.Ratio (%) 11 324 $\times$ 324 219 794 560 406 430 376 428 383 76.8 76.44 12 424 $\times$ 424 260 159 600 317 452 931 450 048 75.45 74.97 13 774 $\times$ 779 466 295 1 093 066 829 270 825 112 75.87 75.49 14 774 $\times$ 779 515 304 1 075 147 783 478 782 257 72.87 72.76 15 465 $\times$ 468 867 441 1 664 608 1 319 629 1 307 906 79.28 78.57 16 399 $\times$ 399 331 663 657 467 528 243 527 043 80.35 80.16 17 557 $\times$ 463 463 213 956 459 743 183 738 101 77.7 77.17 18 973 $\times$ 1 256 551 667 936 162 700 745 699 252 74.85 74.69 AVG 76.65 76.28 表 6 在E3的基础上E1策略或(和) E2策略结合后的优化情况

Table 6 The optimization results with the combination of E1 strategy or (and) E2 strategy based on E3 strategy

基准 EO E1+E3 E2+E3 E1+E2+E3 电路 TOF TWL TOF TWL TOF TWL TOF TWL 11 85 46.7 68 46.4 0 47.5 0 47 12 75 45.9 49 44.4 0 45.6 0 45 13 44 127.1 27 123.7 0 127.4 0 124.6 14 12 110.8 7 110.2 0 110.7 0 110.1 15 32 130.8 13 127.7 0 129.8 0 126.8 16 2 33.9 1 33.9 0 34 0 33.9 17 0 63.4 0 63 0 64.2 0 63.1 18 3 779 80 3 226 80.5 3 165 81 2 762 81.1 Comp. 100 100 67.63 98.91 22.97 100.41 21.64 99.24 表 7 在ISPD98上与5种总体布线算法的对比

Table 7 Comparison between our algorithm and five global routing algorithms on ISPD98

基准 算法 减少率(%) 电路 [3] [5] [2] [4] [6] Ours [3] [5] [2] [4] [6] ibm01 63 332 64 389 62 659 63 720 62 498 58 564 7.53 9.05 6.54 8.09 6.29 ibm02 168 918 171 805 171 110 170 342 169 881 158 383 6.24 7.81 7.44 7.02 6.77 ibm03 146 412 146 770 146 634 147 078 146 458 136 313 6.9 7.12 7.04 7.32 6.93 ibm04 167 101 169 977 167 275 170 095 166 452 153 190 8.32 9.88 8.42 9.94 7.97 ibm06 277 608 278 841 277 913 279 566 277 696 261 606 5.76 6.18 5.87 6.42 5.79 ibm07 366 180 370 143 365 790 369 340 366 133 341 170 6.83 7.83 6.73 7.63 6.82 ibm08 404 714 404 530 405 634 406 349 404 976 379 684 6.18 6.14 6.4 6.56 6.25 ibm09 413 053 414 223 413 862 415 852 414 738 389 281 5.76 6.02 5.94 6.39 6.14 ibm10 578 795 583 805 590 141 585 921 579 870 541 839 6.38 7.19 8.18 7.52 6.56 AVE 6.66 7.47 6.95 7.43 6.61 表 8 在ISPD07上与2种串行算法的总体布线算法的对比

Table 8 Comparison between our algorithm and two serial global routing algorithms on ISPD07

算法 减少率(%) 基准 [6] [8] Ours [6] [8] 电路 TOF TWL TOF TWL TOF TWL TOF TWL TOF TWL 11 0 55.9 0 53.5 0 47 0 15.92 0 12.15 12 0 54 0 51.69 0 45 0 16.67 0 12.94 13 0 134.4 0 130.35 0 124.6 0 7.29 0 4.41 14 0 127.8 0 120.67 0 110.1 0 13.85 0 8.76 15 0 157 0 154.7 0 126.8 0 19.24 0 18.03 16 0 48.6 0 45.99 0 33.9 0 30.25 0 26.29 17 0 78.5 0 74.88 0 63.1 0 19.62 0 15.73 18 31 390 94.9 31 454 104.28 2 762 81.1 91.2 14.54 91.22 22.23 AVE 11.4 17.17 11.4 15.07 表 9 在ISPD07上与2种并行算法的总体布线算法的对比

Table 9 Comparison between our algorithm and two concurrent global routing algorithms on ISPD07

算法 减少率(%) 基准 [11] [12] Ours [11] [12] 电路 TOF TWL TOF TWL TOF TWL TOF TWL TOF TWL 11 0 52.82 0 54.3 0 47 0 11.02 0 13.44 12 0 51.46 0 52.9 0 45 0 12.55 0 14.93 13 0 128.92 0 131 0 124.6 0 3.35 0 4.89 14 0 119.96 0 124 0 110.1 0 8.22 0 11.21 15 0 153.23 0 155 0 126.8 0 17.25 0 18.19 16 228 45.58 228 47 0 33.9 100 25.63 100 27.87 17 0 74.46 0 77.9 0 63.1 0 15.26 0 19 18 31 026 107.22 31 484 108.5 2 762 81.1 91.1 24.36 91.23 25.25 AVE 23.89 14.7 23.9 16.85 -

[1] 徐宁, 洪先龙.超大规模集成电路物理设计理论与方法.清华大学出版社, 2009.Xu Ning, Hong Xian-Long. Very large scale integration physical design theory and method. Tsinghua University Press, 2009. [2] Zhang Y, Xu Y, Chu C. Fastroute 3.0: a fast and high quality global router based on virtual capacity. In: Proceedings of IEEE/ACM International Conference on Computer-Aided Design. New York, USA: IEEE, 2008. 344-349 [3] Roy A J, Markov I L. High-performance routing at the nanometer scale. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(6): 1066-1077 doi: 10.1109/TCAD.2008.923255 [4] Moffitt M D. Maizerouter: Engineering an effective global router. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2008, 27(11): 2017-2026 doi: 10.1109/TCAD.2008.2006082 [5] Ozdal M M, Wong M D F. Archer: A history-based global routing algorithm. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2009, 28(4): 528-540 doi: 10.1109/TCAD.2009.2013991 [6] Chang Y J, Lee Y T, Gao J R, Wu P C, Wang T C. NTHU-Route 2.0: A robust global router for modern designs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2010, 29(12): 1931-1944 doi: 10.1109/TCAD.2010.2061590 [7] Held S, Muller D, Rotter D, Scheifele R, Traub V, Vygen J. Global routing with timing constraints. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2018, 37(2): 406-419 doi: 10.1109/TCAD.2017.2697964 [8] Dai K R, Liu W H, Li Y L. NCTU-GR: efficient simulated evolution-based rerouting and congestion-relaxed layer assignment on 3-D global routing. IEEE Transactions on very large scale integration (VLSI) systems, 2012, 20(3): 459-472 doi: 10.1109/TVLSI.2010.2102780 [9] Wu T H, Davoodi A, Linderoth J T. GRIP: scalable 3D global routing using integer programming. In: Proceedings of ACM/IEEE Design Automation Conference. New York, USA: IEEE, 2009. 320-325 [10] Cho M, Pan D Z. BoxRouter: A new global router based on box expansion and progressive ILP. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2007, 26(12): 2130-2143 doi: 10.1109/TCAD.2007.907003 [11] Liu W H, Kao W C, Li Y L, Chao K Y. NCTU-GR 2.0: multithreaded collision-aware global routing with bounded-length maze routing. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2013, 32(5): 709-722 doi: 10.1109/TCAD.2012.2235124 [12] Han Y, Ancajas D M, Chakraborty K, Roy S. Exploring high-throughput computing paradigm for global routing. IEEE Transactions on Very Large Scale Integration (VLSI) Systems, 2014, 22(1): 155-167 doi: 10.1109/TVLSI.2012.2234489 [13] Teig S L. The X architecture: not your father's diagonal wiring. In: Proceedings of International workshop on System-level interconnect prediction. New York, USA: ACM, 2002. 33-37 [14] Dong J, Zhu H L, Xie M, Zeng X. Graph Steiner tree construction and its routing applications. In: Proceedings of IEEE 10th International Conference on ASIC. New York, USA: IEEE, 2013. 1-4 [15] Hung J H, Yeh Y K, Lin Y C, Huang H H, Hsieh T M. ECO-aware obstacle-avoiding routing tree algorithm. WSEAS Transactions on Circuits and Systems, 2010, 9(9): 567-576 http://d.old.wanfangdata.com.cn/NSTLQK/NSTL_QKJJ0221981287/ [16] Liu G G, Chen G L, Guo W Z. DPSO based octagonal steiner tree algorithm for VLSI routing. In: Proceedings of IEEE 5th International Conference on Advanced Computational Intelligence. New York, USA: IEEE, 2012. 383-387 [17] Ho T Y. A performance-driven X-architecture router based on a novel multilevel framework. Integration, the VLSI Journal, 2009, 42(3): 400-408 doi: 10.1016/j.vlsi.2008.12.002 [18] Ho T Y. A performance-driven multilevel framework for the X-based full-chip router. In: Proceedings of International Workshop on Power and Timing Modeling, Optimization and Simulation. Berlin, Heidelberg: Springer, 2008. 209-218 [19] Hu Y, Jing T, Hong X, Hu X, Yan G. A routing paradigm with novel resources estimation and routability models for X-architecture based physical design. In: Proceedings of International Workshop on Embedded Computer Systems. Berlin, Heidelberg: Springer, 2005. 344-353 [20] Cao Z, Jing T, Hu Y, Shi Y, Hong X, Hu X, Yan G. DraXRouter: Global routing in X-architecture with dynamic resource assignment. In: Proceedings of the 2006 Asia and South Pacific Design Automation Conference. New York, USA: ACM, 2006. 618-623 [21] Liu G G, Guo W Z, Li R R, Niu Y Z, Chen G L. XGRouter: high-quality global router in X-architecture with particle swarm optimization. Frontiers of Computer Science, 2015, 9(4): 576-594 http://d.old.wanfangdata.com.cn/Periodical/zggdxxxswz-jsjkx201504007 [22] ISPD 2007 Global Routing Contest [Online], available: http://www.sigda.org/ispd2007/contest.html, 2007 [23] Liu G G, Huang X, Guo W Z, Niu Y Z, Chen G L. Multilayer obstacle-avoiding X-architecture Steiner minimal tree construction based on particle swarm optimization. IEEE Transactions on Cybernetics, 2015, 45(5): 989-1002 http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=d6b5eb99a0190723fcec4d0ce6de9cb3 [24] ISPD 1998 Global Routing Benchmark Suite [Online], available: http://cseweb.ucsd.edu/kastner/research/labyrinth/, 1998 [25] Kennedy J, Eberhart R C. A discrete binary version of the particle swarm optimization algorithm. In: Proceedings of IEEE International Conference on Systems, Man, and Cybernetics. New York, USA: IEEE, 1997. 4104-4109 [26] Parsopoulos K E, Vrahatis M N. Recent approaches to global optimization problems through particle swarm optimization. Natural Computing, 2002, 1(2-3): 235-306 [27] Pan Q K, Tasgetiren M F, Liang Y C. A discrete particle swarm optimization algorithm for the no-wait flowshop scheduling problem. Computers & Operations Research, 2008, 35(9): 2807-2839 http://www.wanfangdata.com.cn/details/detail.do?_type=perio&id=f0ae38a762e2dd59c2fdc4318af860e1 [28] Guo W Z, Liu G G, Chen G L, Peng S J. A hybrid multi-objective PSO algorithm with local search strategy for VLSI partitioning. Frontiers of Computer Scienceh, 2014, 8(2): 203-216 http://d.old.wanfangdata.com.cn/Periodical/zggdxxxswz-jsjkx201402004 [29] Huang X, Guo W Z, Liu G G, Chen G L. FH-OAOS: a fast 4-step heuristic for obstacle-avoiding octilinear Steiner tree construction. ACM Transactions on Design Automation of Electronic Systems, 2016, 21(3): 48 [30] Huang X, Guo W Z, Liu G G, Chen G L. MLXR: multi-layer obstacle-avoiding X-architecture Steiner tree construction for VLSI routing. Science China Information Sciences, 2017, 60(3): 19102 doi: 10.1007/s11432-015-0850-4?slug=abstract [31] 王东风, 孟丽.粒子群优化算法的性能分析和参数选择.自动化学报, 2016, 42(10): 1552-1561 doi: 10.16383/j.aas.2016.c150774Wang Dong-Feng, Meng Li. Performance analysis and parameter selection of PSO algorithms. Acta Automatica Sinica, 2016, 42(10): 1552-1561 doi: 10.16383/j.aas.2016.c150774 [32] 吕柏权, 张静静, 李占培, 刘廷章.基于变换函数与填充函数的模糊粒子群优化算法.自动化学报, 2018, 44(1): 74-86 doi: 10.16383/j.aas.2018.c160547Lv Bai-Quan, Zhang Jing-Jing, Li Zhan-Pei, Liu Ting-Zhang. Fuzzy partical swarm optimization based on filled function and transformation function. Acta Automatica Sinica, 2018, 44(1): 74-86 doi: 10.16383/j.aas.2018.c160547 [33] Zhang W, Zhang H, Liu J, Li K, Yang D, Tian H. Weather prediction with multiclass support vector machines in the fault detection of photovoltaic system. IEEE/CAA Journal of Automatica Sinica, 2017, 4(3): 520-525 doi: 10.1109/JAS.2017.7510562 [34] Han Z, Zhao J, Wang W. An optimized oxygen system scheduling with electricity cost consideration in steel industry. IEEE/CAA Journal of Automatica Sinica, 2017, 4(2): 216-222 doi: 10.1109/JAS.2017.7510439 [35] Tang Y, Luo C, Yang J, He H. A chance constrained optimal reserve scheduling approach for economic dispatch considering wind penetration. IEEE/CAA Journal of Automatica Sinica, 2017, 4(2): 186-194 doi: 10.1109/JAS.2017.7510499 [36] Rudolph G. Convergence analysis of canonical genetic algorithms. IEEE Transactions on Neural Networks, 1994, 5(1): 96-101 [37] Lv H, Zheng J, Wu J, Zhou C, Li K. The convergence analysis of genetic algorithm based on space mating. In: Proceedings of IEEE 5th International Conference on Natural Computation. New York, USA: IEEE, 2009. 557-562 -

下载:

下载: