-

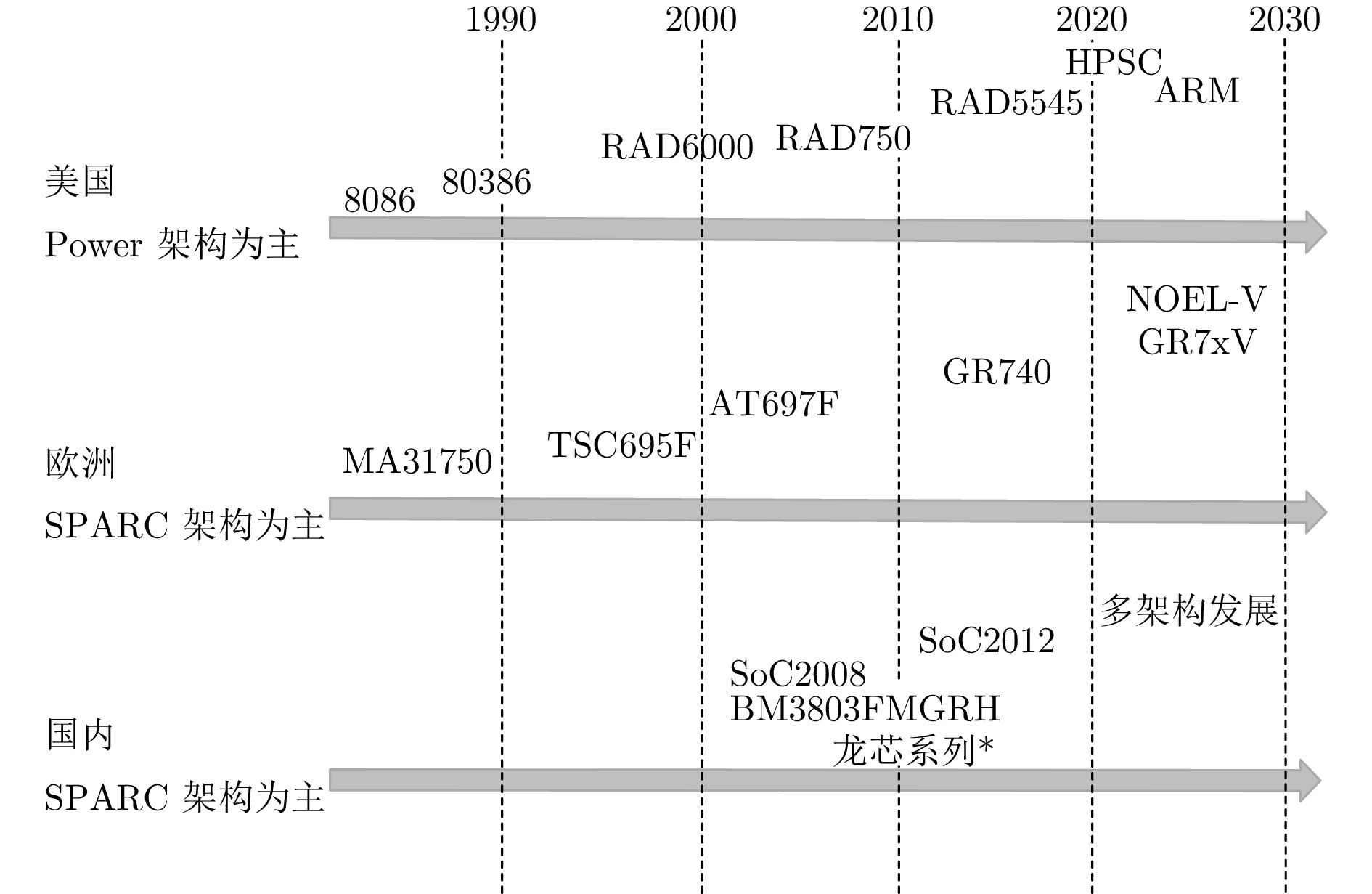

摘要: 本文系统回顾美国、欧洲及我国在宇航用处理器领域的技术演进, 重点分析了基于PowerPC架构的美国代表性处理器产品以及采用SPARC架构的欧洲与我国典型处理器方案. 研究揭示, 未来宇航用处理器的发展将显著分化为通用型与智能型两大技术路线. 通用型宇航用处理器将呈现高性能(如提升多核并行计算能力)、高集成度(如实现系统级芯片SoC)、高可靠性(如强化抗辐射设计)及低功耗的协同发展趋势; 而智能型处理器则将侧重于提升在轨实时智能信息处理能力.Abstract: This paper provides a systematic review of the technological evolution of aerospace processors in the United States, Europe, and China. It primarily analyzes representative U.S. processor products based on the PowerPC architecture, as well as typical European and Chinese processor solutions that utilize the SPARC architecture. The research identifies that the future development of aerospace processors is expected to diverge into two main technical directions: general-purpose and intelligent processors. General-purpose aerospace processors will follow a coordinated trend of increased performance (such as enhanced multi-core parallel computing capabilities), higher integration (such as system-on-chip designs), improved reliability (such as enhanced radiation-hardened designs), and reduced power consumption. In contrast, intelligent processors will concentrate on advancing real-time intelligent information processing capabilities for space applications.

-

Key words:

- aerospace processor /

- processor architecture /

- PowerPC /

- SPARC /

- RISC-V

-

表 1 美国宇航用处理器各指标对比

Table 1 Comparison of various indicators of U.S. aerospace processor

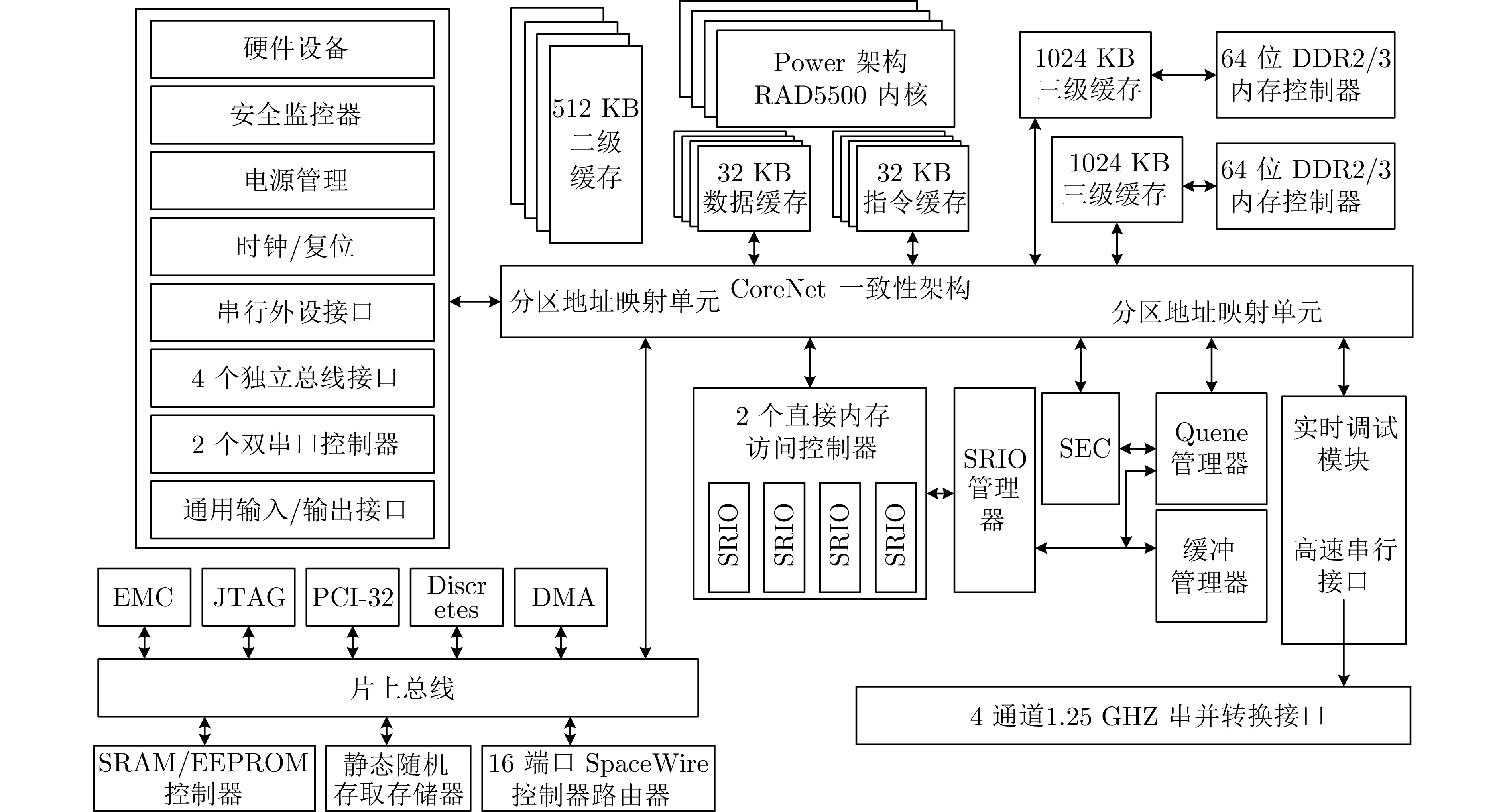

处理器 RAD 6000 RAD 750 RAD 5510 RAD 5545 架构 PowerPC PowerPC PowerPC PowerPC 内核 RS6000 Power 750 Power e5500 Power e5500 主频 33 MHz 132–233 MHz 466 MHz 466 MHz 核心数量 1 1 1 4 位数 32 32 64 64 TID 100K rad(Si) 1M rad(Si) 1M rad(Si) 1M rad(Si) SEU(错误/(器件·天)) $ \leq $ 7.4E $ - $ 10 $ \leq $ 1.6E $ - $ 10 $ \leq $ 8E $ - $ 14 $ \leq $ 8E $ - $ 14 SEL - - - - 性能 35 MIPS 200–400 MIPS 1.4 GOPS 4.6 GOPS 功耗 - 5 W 11.5 W 17.7 W 表 2 欧洲宇航用处理器各指标对比

Table 2 Comparison of various indicators of European aerospace processor

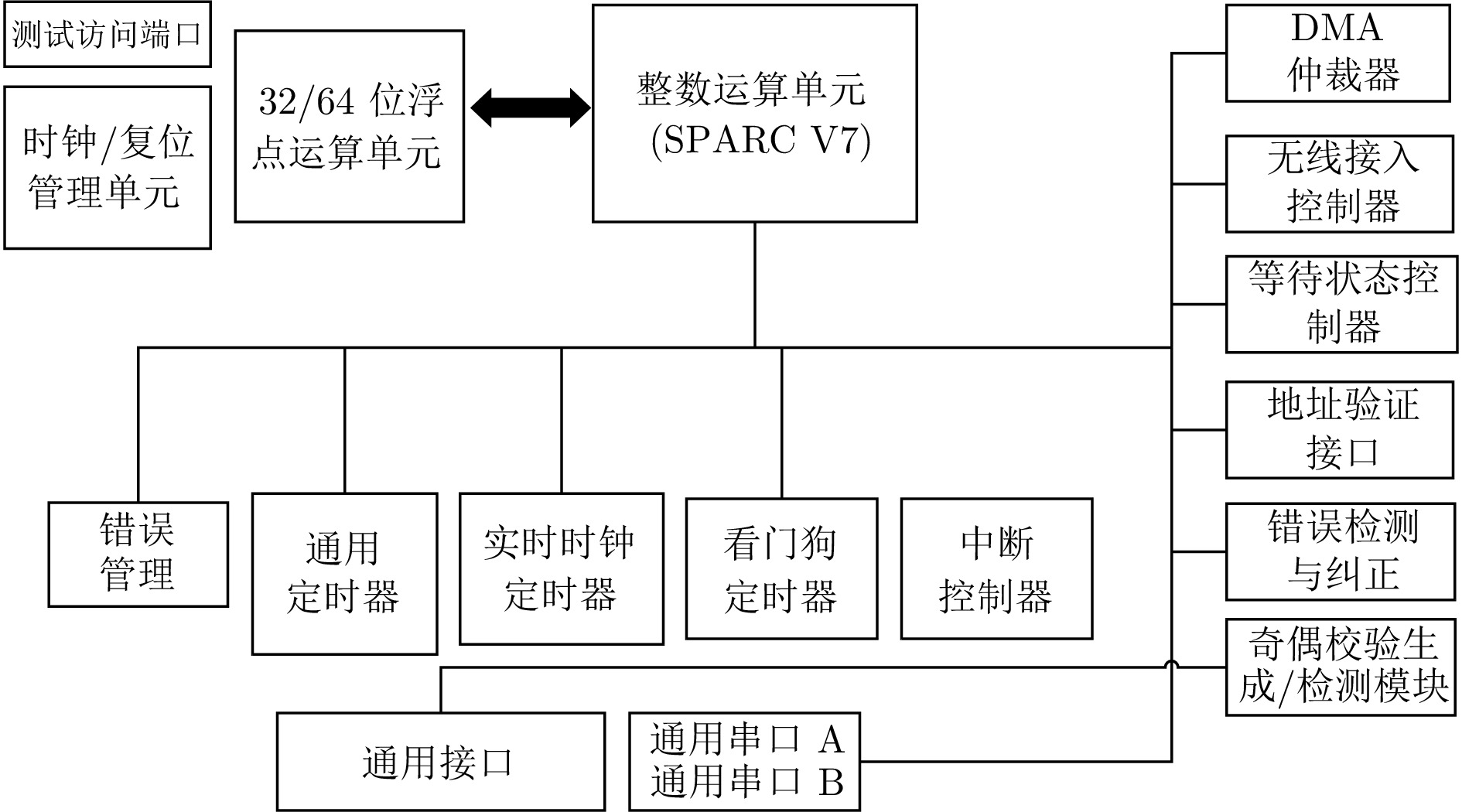

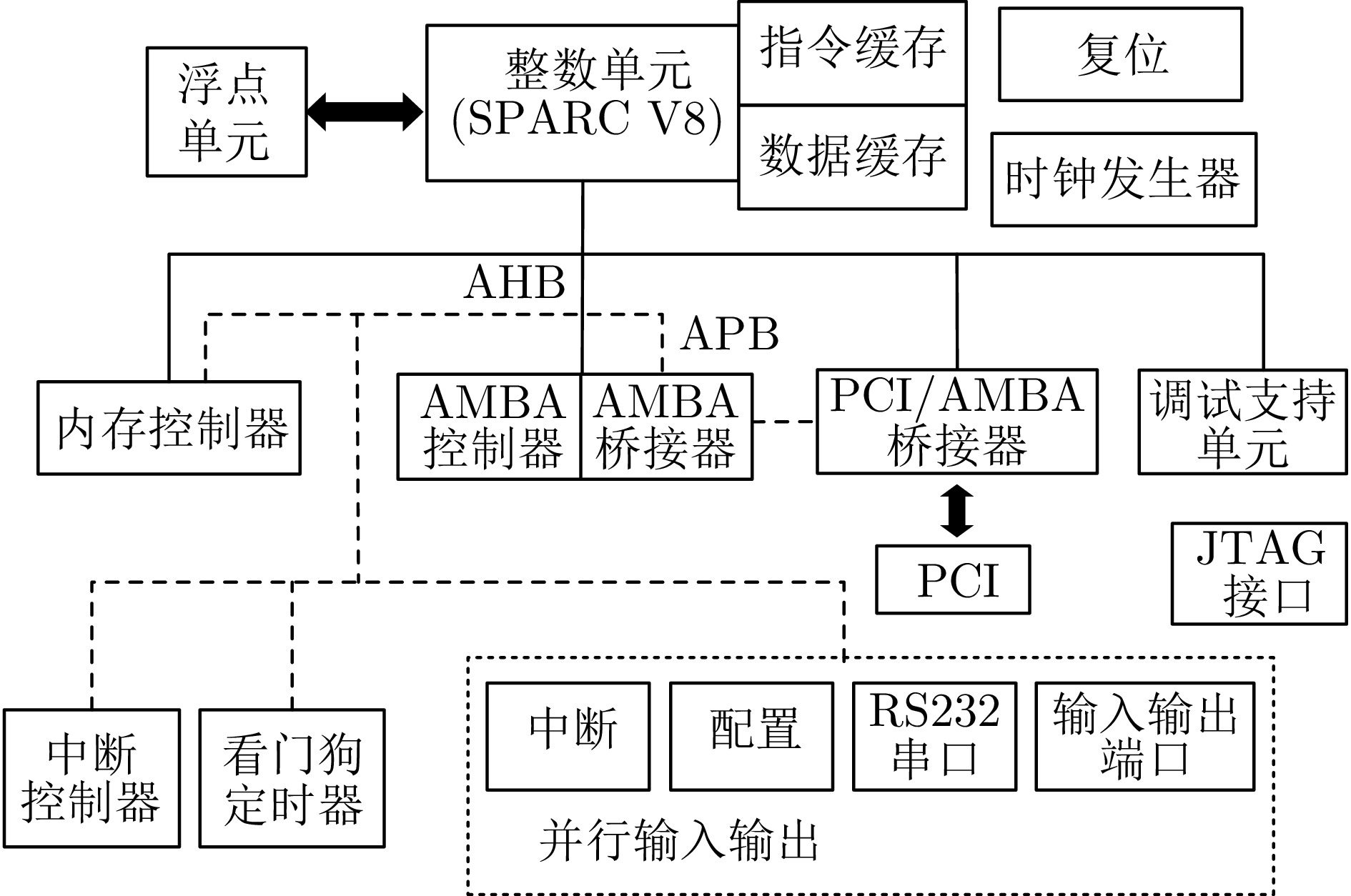

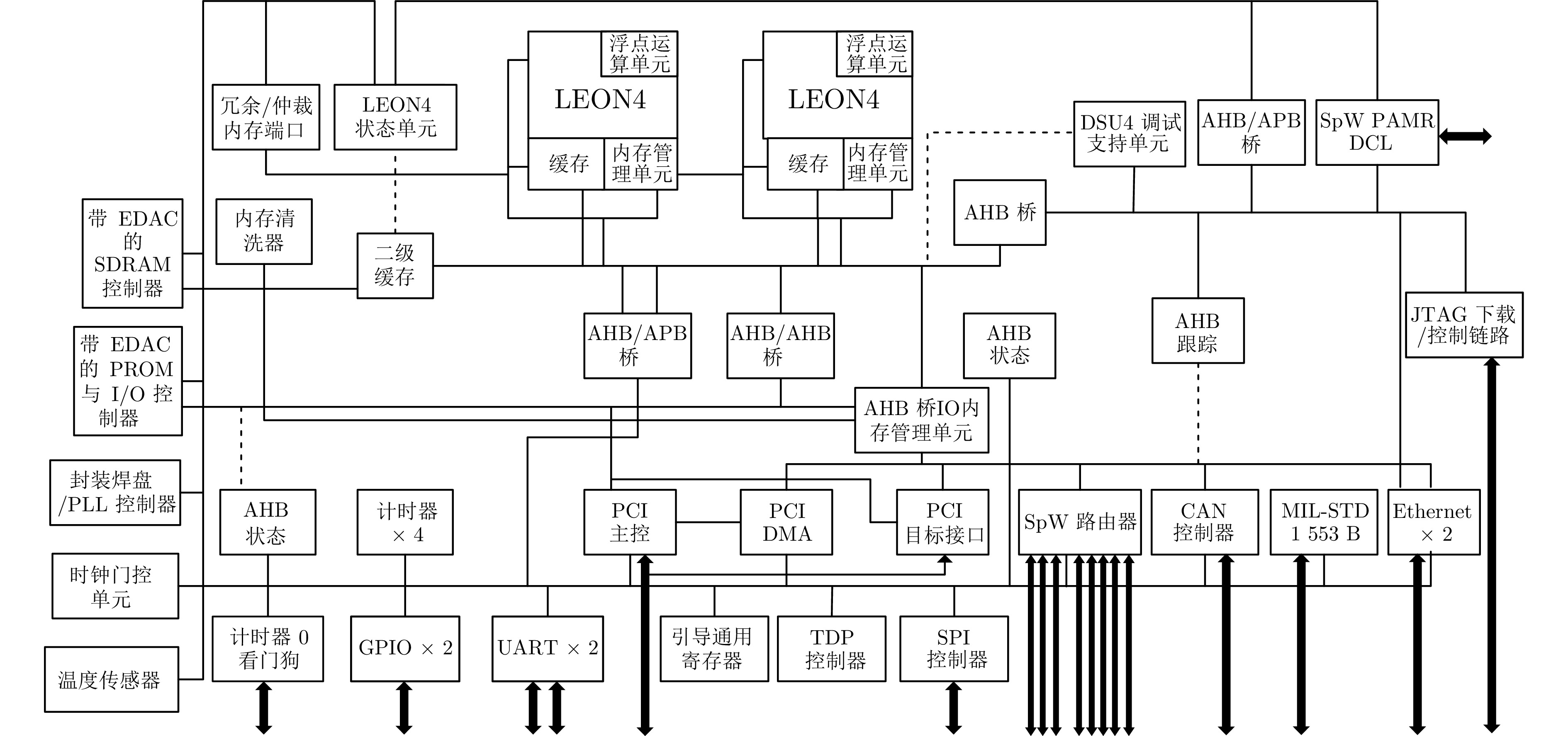

处理器 MA31750 TSC695F AT697F GR740 NOEL-V 架构 - SPARC V7 SPARC V8 SPARC V8 RISC-V 主频 25 MHz 25 MHz 100 MHz 250MHz - 内核 - ERC32 LEON2 LEON4-FT - 核心数量 1 1 1 4 4 流水线 - 4 5 7 7 位数 32 32 32 32 64 性能(Dhrystone/core) - 25 MIPS 86 MIPS 1.7DMIPS - TID $ \geq $ 300K $ \geq $ 300K $ \geq $ 300K $ \geq $ 300K - SEU(errors/card-day) $ \leq $ 6E $ - $ 7 $ \leq $ 3E $ - $ 8 $ \leq $ 1E $ - $ 5 $ \leq $ 1E $ - $ 5 - SEL - $ \geq $ 100 $ \geq $ 70 ≥ 125 - 功耗 - $ \leq $ 1.5 W $ \leq $ 1 W ≤ 1.8W - 工艺 - 500 nm (MG2RT) 180 nm (CMOS) 65nm(CMOS) - 表 3 龙芯系列产品架构指标

Table 3 Loongson series product architecture indicators

处理器 1J 1F04 1F300 1E03 1E300 1E1000 架构 MIPS MIPS MIPS MIPS MIPS MIPS L1 Cache - - - 8K+8K 16K+16K 32K+32K L2 Cache - - - - - 1M 核心 1 1 1 1 1 2 主频 10 MHz 33 MHz 100 MHz 100 MHz 200 MHz 1 GHz 内存接口 - SRAM SRAM、SDRAM SDRAM SDRAM DDR2/3 SpaceWire - - $ \checkmark $ - - $ \checkmark $ 1553 - $ \checkmark $ $ \checkmark $ - - - PCI - $ \checkmark $ $ \checkmark $ $ \checkmark $ $ \checkmark $ - UART $ \checkmark $ $ \checkmark $ $ \checkmark $ $ \checkmark $ $ \checkmark $ $ \checkmark $ I $ ^{2} $ C $ \checkmark $ - - $ \checkmark $ $ \checkmark $ $ \checkmark $ SPI $ \checkmark $ - - $ \checkmark $ $ \checkmark $ $ \checkmark $ 表 4 我国宇航用处理器各指标对比

Table 4 Comparison of various indicators of China’s aerospace processor

处理器 SoC2008 SoC2012 BM3803MGRH LS1E LS1F 架构 SPARC V8 SPARC V8 SPARC V8 MIPS MIPS 主频 100 MHz 100 MHz 100 MHz 200 MHz 100 MHz 核心数量 1 4 1 1 1 流水线 7 7 7 7 7 性能 0.86 DMIPS 3 DMIPS 0.85 DMIPS - - TID $ \geq $ 100K $ \geq $ 200K $ \geq $ 100K $ \geq $ 300K $ \geq $ 100K SEU $ \leq $ 1E $ - $ 7 $ \leq $ 3E $ - $ 8 $ \leq $ 5E $ - $ 5 $ \leq $ 6.5E $ - $ 5 $ \leq $ 1E $ - $ 5 SEL $ \geq $ 100 $ \geq $ 100 $ \geq $ 75 $ \geq $ 75 $ \geq $ 75 功耗 $ \leq $ 0.7 W $ \leq $ 1 W $ \leq $ 1 W $ \leq $ 3 W $ \leq $ 3 W 工艺 130 nm (CMOS) 130 nm (CMOS) - 180 nm (CMOS) 180 nm (CMOS) -

[1] 袁利, 姜甜甜, 魏春岭, 杨孟飞. 空间控制技术发展与展望. 自动化学报, 2023, 49(3): 476−493Yuan Li, Jiang Tian-Tian, Wei Chun-Ling, Yang Meng-Fei. Advances and perspectives of space control technology. Acta Automatica Sinica, 2023, 49(3): 476−493 [2] 杜永浩, 邢立宁, 姚锋, 陈盈果. 航天器任务调度模型、算法与通用求解技术综述. 自动化学报, 2021, 47(12): 2715−2741 doi: 10.16383/j.aas.c190656Du Yong-Hao, Xing Li-Ning, Yao Feng, Chen Ying-Guo. Survey on models, algorithms and general techniques for spacecraft mission scheduling. Acta Automatica Sinica, 2021, 47(12): 2715−2741 doi: 10.16383/j.aas.c190656 [3] Marshall J R, Robertson J. An embedded microcontroller for spacecraft applications. In: Proceedings of the 2006 IEEE Aerospace Conference. Big Sky, MT, USA: IEEE, 2006: 9 pp. [4] RAD750 Radiation-hardened PowerPC Microprocessor. BAE Systems, Jul. 2008.[Online], available: https://www.baesystems.com/en-us/dam. [5] RAD6000 Space Computers. BAE Systems, Aug. 2004.[Online], available: https://foro.sondasespaciales.com/index.php?action=dlattach;topic=5280.0;attach=334. [6] 覃辉, 于立新.宇航处理器技术发展趋势和特点". 第六届航天电子战略研究论坛论文集(2019年第01期 总第65期 2019年03月季刊). 北京, 我国, 2019. 54-58Qin H, Yu L X. Development Trends and Characteristics of Aerospace Processor Technology. In: Proceedings of The Sixth Aerospace Electronics Strategy Research Forum Papers (Issue 01, 2019, No.65, 2019, March Quarterly). Beijing, China, 2019. 54-58 [7] RAD5510 Single-core System-on-ship Power Architecture Processor. BAE Systems, [Online], available: https://satsearch.co/products/bae-systems-rad5510-single-core, December 2, 2025. [8] RAD5545 Multi-core System-on-ship Power Architecture Processor. BAE Systems, [Online], available: https://satsearch.co/products/bae-systems-rad5545-multi-core-system, December 2, 2025. [9] Schwaller B, Holtzman S, George A D. Emulation-based performance studies on the HPSC space processor. In: Proceedings of the 2019 IEEE Aerospace Conference. Big Sky, MT, USA: IEEE, 2019. 1-11 [10] Guertin S M, Some R, Nsengiyumva P, et al. Radiation specification and testing of heterogeneous microprocessor SOCs. In: Proceedings of the 2019 19th European Conference on Radiation and Its Effects on Components and Systems (RADECS). Montpellier, FRANCE: IEEE, 2019. 1-7 [11] Gaisler J. LEON SPARC Processor The past, present and future. RAMP Winter Retreat, Berkeley. 2007 [12] MICROCHIP. Rad-Hard 32-bit SPARC Embedded Processor-TSC695F Rev 4118J-AERO-08/04.[Online], available: www.microchip.com/wwwproducts/en/TSC695F, December 2, 2025. [13] Atmel Corporation. TSC695F SPARC 32-bit Space Processor User Manual.[Online], available: https://ww1.microchip.com/downloads/en/DeviceDoc, December 2, 2025. [14] MICROCHIP. Rad-Hard 32-bit SPARC V8 Processor. Rev. 7703E-AERO-08/11.[Online], available: www.microchip.com/wwwproducts/en/AT697F, December 2, 2025. [15] Atmel Corporation. Rad-Hard 32-bit SPARC V8 Processor AT697E User Manual.[Online], available: https://www.alldatasheet.com, December 2, 2025. [16] Cobham Gaisler AB. GR712RC Dual-Core LEON3FT SPARC V8 Processor Data Sheet.[Online], available: https://download.gaisler.com/products/gr712rc/doc/gr712rc-, December 2, 2025. [17] Tambara L A, Hernandez F, Sturesson F, Hjorth M, Andersson J, Weigand R. Single Event Effect Characterization of the GR740 Rad-Hard Quad-Core LEON4FT System-on-Chip. In: Proceedings of the 2019 19th European Conference on Radiation and Its Effects on Components and Systems (RADECS). Montpellier, France: IEEE, 2019. 1-6 [18] COBHAM. GR740 Radiation Summary[Online], available: www.gaisler.com.2019, December 2, 2025 [19] Andersson J, Hjorth M, Johansson F, Habinc S. LEON Processor Devices for Space Missions: First 20 Years of LEON in Space. In: Proceedings of the 2017 6th International Conference on Space Mission Challenges for Information Technology (SMC-IT). New York, NY, USA: IEEE Computer Society, 2017. 136-141 [20] Andersson J. Development of a NOEL-V RISC-V SoC Targeting Space Applications. In: Proceedings of the 2020 50th Annual IEEE/IFIP International Conference on Dependable Systems and Networks Workshops (DSN-W). Valencia, Spain: IEEE, 2020. 66-67 [21] Jonsson J, Toselli M. White-box Verification of a RISC-V Processor: NOEL-V, 2022 [22] Wessman N J, Malatesta F, Andersson J, et al. De-RISC: the first RISC-V space-grade platform for safety-critical systems. In: Proceedings of the 2021 IEEE Space Computing Conference (SCC). Laurel, MD, USA: IEEE, 2021. 17-26 [23] Li Y, Zhu X, Zhang W, et al. Design and verification of CPU for teaching based on sparc V8. In: Proceedings of the 2013 Fourth International Conference on Intelligent Systems Design and Engineering Applications. Zhangjiajie, China: IEEE, 2013. 236-240 [24] 北京控制工程研究所. SoC2008型32位片上系统芯片用户手册. V3.0. 2013Beijing Institute of Control Engineering. User Manual for SoC2008 32-bit System on Chip V3.0, 2013. [25] 北京控制工程研究所. 四核SoC2012型32位片上系统芯片用户手册. V1.0. 2013Beijing Institute of Contro Engineering. User Manual for Quad Core SoC2012 32-bit System on Chip V1.0. 2013 [26] 北京微电子技术研究所. BM3803FMGRH产品使用手册Beijing Microelectronics Technology Institute. Bm3803fmgrh product manual [27] 龙芯中科技术有限公司. 国产化自主安全–龙芯抗辐照芯片技术白皮书. 2018Loongson Technology Corporation Limited. Domestic independent safety – white paper on radiation resistant chip technology of Loongson. 2018 [28] 徐帅, 林宝军, 刘迎春, 赵帅. 基于龙芯宇航级芯片的 BSP 开发和移植. 计算机工程与科学, 2020, 42(04): 571Xu S, Lin B J, Liu Y C, Zhao S. Development and transplantation of BSP based on Godson aerospace chip. Computer Engineering & Science, 2020, 42(04): 571 [29] 王瑛, 严涛, 王磊. 空间智能导航技术发展现状与趋势分析. 空间控制技术与应用, 2022, 48(5): 9−17Wang Y, Yan T, Wang L. Development status and trend analysis of space intelligent navigation technology. Aerospace Control and Application, 2022, 48(5): 9−17 [30] David P, Andrew W. The RISC-V Reader: An Open Architecture Atlas. California: Strawberry Canyon. 2017 [31] Mascio S D, Menicucci A, Gill E, Furano, G, Monteleone C. Leveraging the Openness and Modularity of RISC-V in Space. Journal of Aerospace Information Systems, 2019, 16(11): 454−472 doi: 10.2514/1.I010735 [32] 孙川川, 高瑛珂, 李圣龙, 赵云富, 梁贤赓. 面向宇航应用的高可靠 SoC 异常处理系统设计. 空间控制技术与应用, 2020, 46(3): 78 doi: 10.3969/j.issn.1674-1579.2020.03.012Sun C C, Gao Y K, Li S L, Zhao Y F, Liang X G. Design of highly reliable SOC exception handling system for aerospace applications. Aerospace Control and Application, 2020, 46(3): 78 doi: 10.3969/j.issn.1674-1579.2020.03.012 [33] 魏肖彤, 许浩博, 尹春笛, 黄俊培, 孙文昊, 徐文浚, 等. 天基计算芯片:现状、趋势与关键技术. 电子与信息学报, 2025, 47(09): 2963−2978Wei X T, Xu H B, Yin C D, Huang J P, Sun W H, Xu W J, et al. Space-based Computing Chips: Current Status, Trends and Key Technique. Journal of Electronics & Information Technology, 2025, 47(09): 2963−2978 [34] Lüdtke D, Firchau T, Cortes C G, Lund A, Nepal, A M, Elbarrawy M M, et al. ScOSA on the way to orbit: Reconfigurable high-performance computing for spacecraft. In: Proceedings of the 2023 IEEE Space Computing Conference (SCC). Pasadena, CA, USA: IEEE, 2023. 34-44 [35] Li L, He J, Xu D X, Chen W Y, Yu J P, Li H. Design of High-Performance and General-Purpose Satellite Management Unit Based on Rad-Hard Multi-Core SoCand Linux. Aerospace, 2023, 10(2): 201 doi: 10.3390/aerospace10020201 [36] Hennessy, John L., Patiterson, David A.. A New Golden Age for Computer Architecture. Communications of the ACM, 2019, 62(2): 48−60 doi: 10.1145/3282307 [37] Leon V, Lentaris G, Soudris D, Furano G, Tavoularis A, et al. Improving performance-power-programmability in space avionics with edge devices: VBN on Myriad2 SoC. ACM Transactions on Embedded Computing Systems (TECS), 2021, 20(3): 1−23 doi: 10.1145/3440885 [38] Perryman N, Franconi N, Crum G, et al. SpaceCube GHOST: A Resilient Processor for Low-Power, High-Reliability Space Computing. In: Proceedings of the 2024 IEEE Aerospace Conference. Big Sky, MT, USA: IEEE, 2024. 1-11 [39] 李韶光, 刘雷, 郎金鹏, 王建国. CPU发展概述及国产化之路. 网络空间安全, 2020, 11(4): 114−117Li S G, Liu L, Lang J P, Wang J G. Overview of CPU development and localization. Cyberspace Security, 2020, 11(4): 114−117 [40] Di M S, Menicucci A, Gi ll, E, Furano G, Monteleone, C. Open-source IP cores for space: A processor-level perspective on soft errors in the RISC-V era. Computer Science Review, 2021, 39: 100349 doi: 10.1016/j.cosrev.2020.100349 [41] Liu B, Yang M F, Wang Y, Yuan L, Liu C W, Xu J, et al. A lightweight data-voting strategy for triple-modular redundant control computers. Science China Technological Sciences, 2022, 65(2): 419−431 doi: 10.1007/s11431-021-1928-0 [42] Liang, Z N, Nian J W, Liu H J, Wang X R, Ya ng, M F. C-DMR: a cache-based fault-tolerant protection method for register file. The Journal of Supercomputing, 2023, 79(4): 4383−4397 doi: 10.1007/s11227-022-04836-2 [43] S. Alcaide, L. Kosmidis, C. Hernandez, and J. Abella. Achieving Diverse Redundancy for GPU Kernels. IEEE Transactions on Emerging Topics in Computing, 2021, 10(2): 618−634 doi: 10.1109/tetc.2021.3101922 [44] S. Venkatesha and R. Parthasarathi. Survey on redundancy based fault tolerance methods for processors and hardware accelerators: trends in quantum computing, heterogeneous systems and reliability. ACM Computing Surveys, 2024, 56(11): 1−76 doi: 10.1145/3663672 [45] 虞志刚, 冯旭, 陆洲, 高吉星, 丁文慧. 宇航级处理器发展现状与趋势. 天地一体化信息网络, 2023, 4(1): 50−58Yu Z G, Feng X, Lu Z, Gao J X, Ding W H. Development status and trend of aerospace grade processors. Space-Integrated-Ground Information Networks, 2023, 4(1): 50−58 [46] Xie R C, Tang Q Q, Wang Q N, Liu X, Yu F R, Huang T. Satellite-terrestrial integrated edge computing networks: Architecture, challenges, and open issues. IEEE Network, 2020, 34(3): 224−231 doi: 10.1109/MNET.011.1900369 [47] Hu Y, Liu Y, Liu Z. A survey on convolutional neural network accelerators: GPU, FPGA and ASIC. In: Proceedings of the 2022 14th International Conference on Computer Research and Development (ICCRD). Shenzhen, China: IEEE, 2022. 100-107 [48] 朱海涛. AI芯片的应用与发展趋势. 我国安全防范技术与应用, 2019, 5: 44−49 doi: 10.3969/j.issn.1672-1470.2019.05.009Zhu H T. Application and development trend of AI chip. China Security Protection Technology And Application, 2019, 5: 44−49 doi: 10.3969/j.issn.1672-1470.2019.05.009 [49] 汪春霆, 翟立君, 徐晓帆. 天地一体化信息网络发展与展望. 无线电通信技术, 2020, 46(5): 491−504Wang C T, Zhai L J, Xu X F. Development and Prospect of space earth integrated information network. Radio Communications Technology, 2020, 46(5): 491−504 [50] Wu Q, Shen Y F, and Zhang M Q. 2022. Heterogeneous Computing and Applications in Deep Learning: A Survey. In: Proceedings of the 5th International Conference on Computer Science and Software Engineering (CSSE '22). New York, NY, USA: Association for Computing Machinery, 2022. 383–387. https://doi.org/10.1145/3569966.3570075 [51] Vandame P, Noé A, Čech J, Apostol L, Prieur C, McNamara K, et al. Assessing the potential of Qormino processor for embedded AI on board a CubeSat. IEEE Journal on Miniaturization for Air and Space Systems, 2022, 3(3): 121−128 doi: 10.1109/JMASS.2022.3202438 [52] Furano G, Di Mascio S, Menicucci A, Monteleone C. A European roadmap to leverage RISC-V in space applications. In: Proceedings of the 2022 IEEE Aerospace Conference (AERO). Big Sky, Montana, USA: IEEE, 2022. 1-7 [53] Mezger B W, Santos D A, Dilillo L, Zeferino C A. A, Melo D R. A survey of the RISC-V architecture software support. IEEE Access, 2022, 10: 51394−51411 doi: 10.1109/ACCESS.2022.3174125 [54] Cappellone D, Di Mascio S, Furano G, Menicucci A, Ottavi M. On-board satellite telemetry forecasting with RNN on RISC-V based multicore processor. In: Proceedings of the 2020 IEEE International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT). ESA-ESRIN, Frascati, Italy: IEEE, 2020. 1-6 [55] Liu Y Q, Han Y H, Li H X, Gu S H, Qiu J B, Li T. Computing over Space: Status, Challenges, and Opportunities, Engineering, https://doi.org/10.1016/j.eng.2025.06.005 [56] Yin Z S, Wu C H, Guo C B, Li Y C, Xu M W, Gao W W, et al. A comprehensive survey of orbital edge computing: Systems, applications, and algorithms. Chinese Journal of Aeronautics, 2025, 38(7): 103316 doi: 10.1016/j.cja.2024.11.026 [57] Dunkel E R, Swope J, Candela A, West L, Chien S A, Towfic Z, et al. Benchmarking deep learning models on myriad and snapdragon processors for space applications. Journal of Aerospace Information Systems, 2023, 20(10): 660−674 doi: 10.2514/1.I011216 [58] Yu X C, Zhuang S F, Liu T, Wang Y, Yang B X. High Reliability FPGA Dynamic Partial Reconfiguration for Aerospace Application. Spacecraft Recovery & Remote Sensing, 2019, 40(3): 42−43 -

计量

- 文章访问数: 291

- HTML全文浏览量: 288

- 被引次数: 0

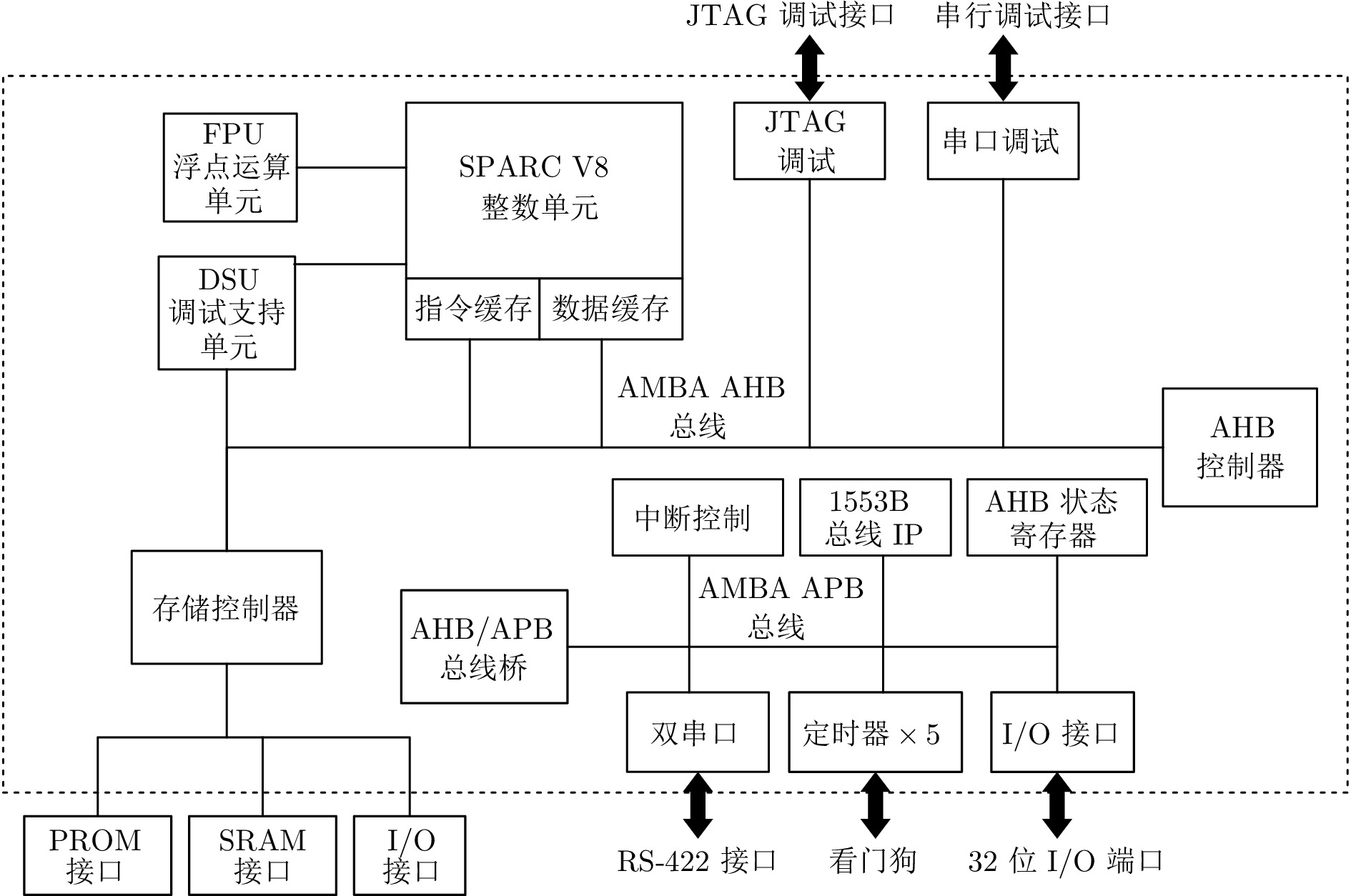

下载:

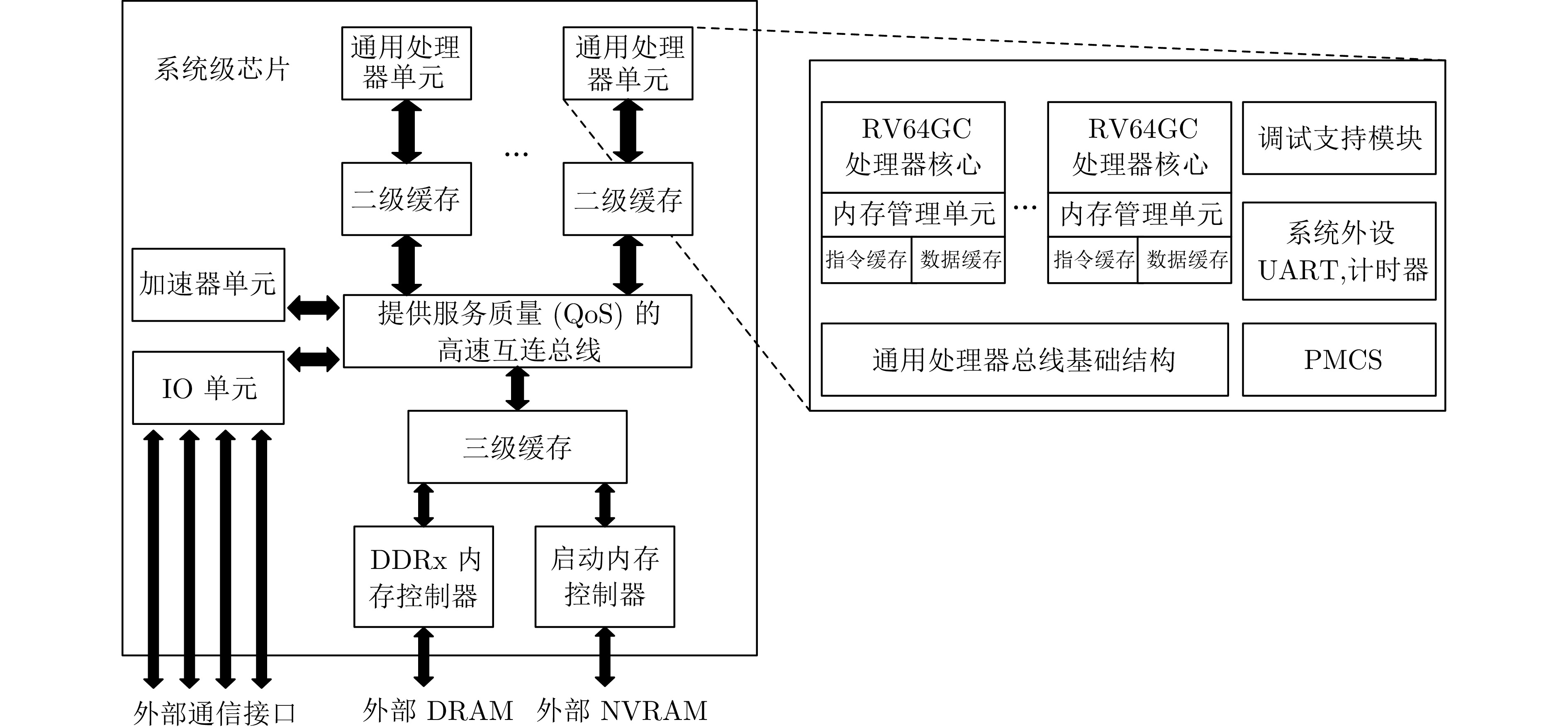

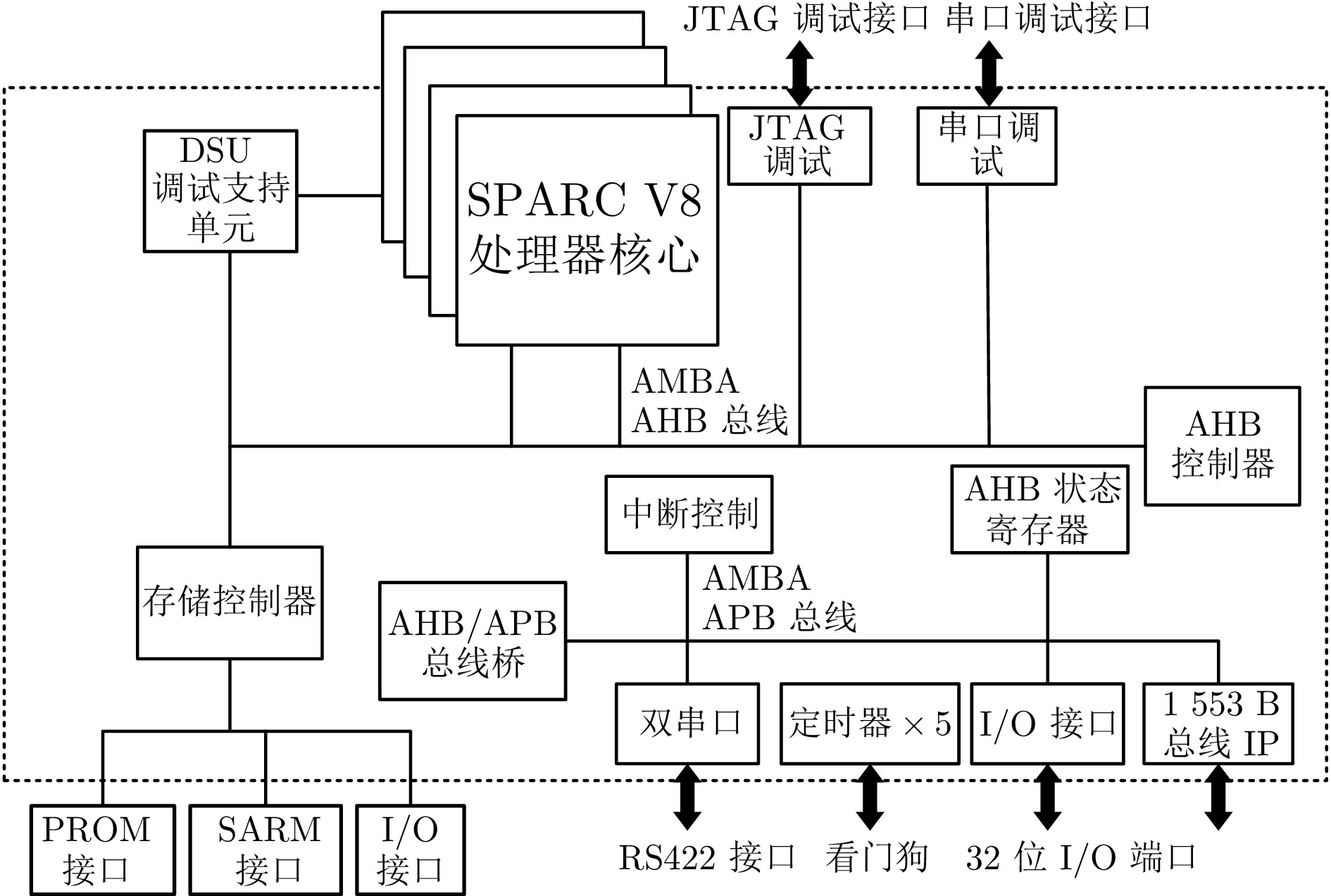

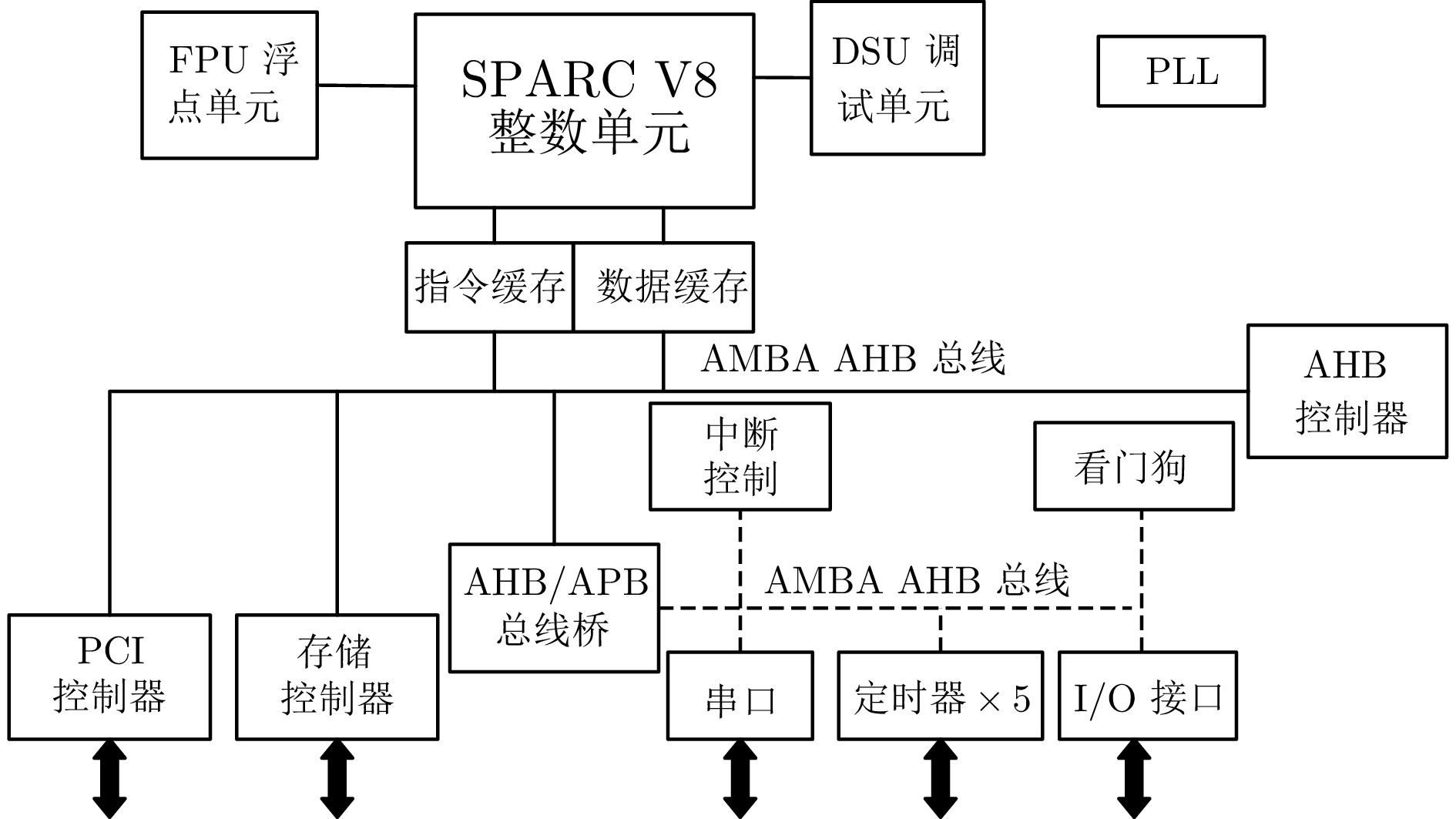

下载: